【導讀】信號沿傳輸線向前傳播時,每時每刻都會感受到一個瞬態阻抗,這個阻抗可能是傳輸線本身的,也可能是中途或末端其他元件的。對于信號來說,它不會區分是什么,信號所感受到的只有阻抗。如果信號感受到的阻抗是恒定的,那么他就會正常向前傳播,只要感受到的阻抗發生變化,信號都會發生反射。這些因素可能包括過長的走線,末端匹配的傳輸線,過量的電容或電感及阻抗失配。

本文要點:

1,介紹信號分列反射的具體表現;

2,結合具體電路分析。

信號沿傳輸線向前傳播時,每時每刻都會感受到一個瞬態阻抗,這個阻抗可能是傳輸線本身的,也可能是中途或末端其他元件的。對于信號來說,它不會區分是什么,信號所感受到的只有阻抗。如果信號感受到的阻抗是恒定的,那么他就會正常向前傳播,只要感受到的阻抗發生變化,信號都會發生反射。這些因素可能包括過長的走線,末端匹配的傳輸線,過量的電容或電感及阻抗失配。

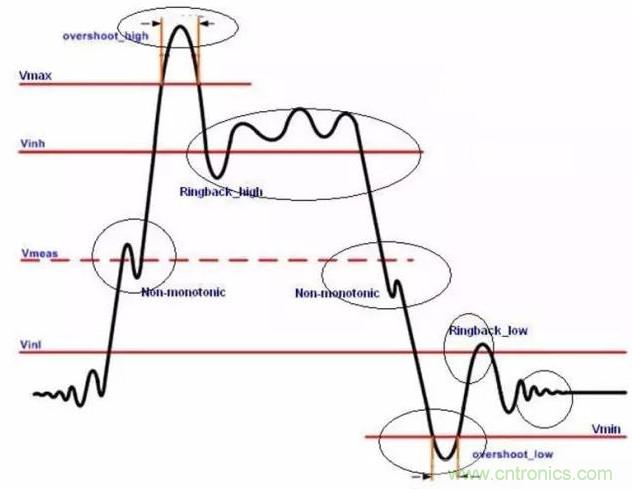

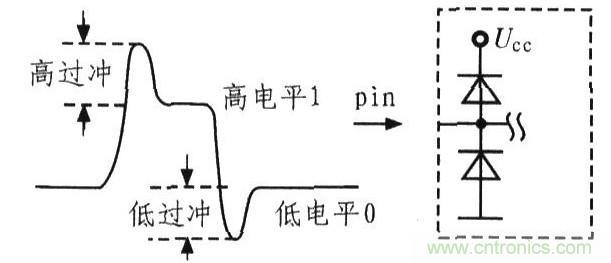

反射會造成信號過沖overshoot、下沖undershoot、振鈴ringing、邊沿遲緩也就是階梯電壓波。過沖是振鈴的欠阻尼狀態,邊沿遲緩是振鈴的過阻尼狀態。當信號的第一個波峰超過原來設定的最大值。過沖是指信號跳變的第一個峰值或谷值,它是在電源電平之上或參考地電平之下的額外電壓效應;

邊沿遲緩我們也成為臺階,回勾現象,其危險主要是會造成誤觸發。

下沖是指信號跳變的下一個谷值或峰值。過沖與下沖都是不利的因素,過大的過沖電壓經常長期性地沖擊會造成器件的損壞,如上圖所示。嚴重的下沖會超過接收器件的門限而導致電路的邏輯錯誤。

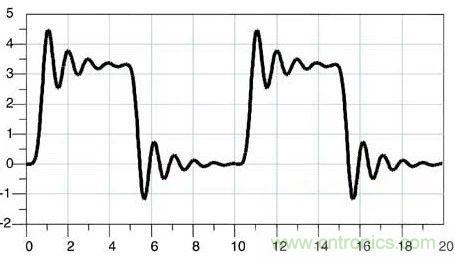

如果信號在驅動器和接收器之間來回多次反射,就會產生振鈴現象,這增加了信號穩定所需要的時間,從而也影響了系統穩定的時序。

細節處如下圖,

電路設計Tips:

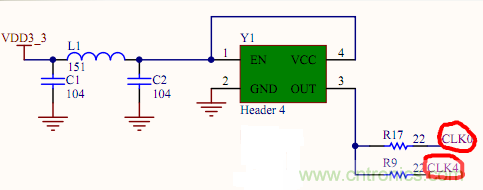

一般做電路設計中,如果時鐘信號鏈路比較長,會在時鐘輸出信號上串接一個小電阻,比如22歐姆或者33歐姆。

至于為什么,很多成熟設計都是這么做,算是一個經驗設計方法。實際上,其實這個小電阻的作用就是為了解決信號反射問題。而且隨著電阻的加大,振鈴會消失,但你會發現信號上升沿不再那么陡峭了,串聯電阻是為了減小反射波,避免反射波疊加引起過沖。這個解決方法叫阻抗匹配,一定要注意阻抗匹配,阻抗在信號完整性問題中占據著極其重要的地位。

來源:面包板社區博主 啟芯 的博客

推薦閱讀: